Les modules 400G ZR QSFP-DD DCO sont basés sur le DP- 16QAM prenant en charge une bande C étendue, une détection cohérente de diversité de polarisation et une égalisation de liaison électronique avancée. La compensation de dispersion chromatique peut être appliquée au côté réception du démodulateur. Ce module est géré en utilisant l'interface à deux fils qui est spécifiée dans la spécification de l'interface de gestion commune (CMIS).

Le module utilise un connecteur QSFP-DD spécification matérielle QSFP-DD MSA à 76 broches pour toutes les interfaces électriques avec la carte hôte, tandis que les interfaces optiques côté ligne sont fournies par les réceptacles optiques sur le QSFP-DD. Le module peut être réparti en trois parties fonctionnelles: chemin TX, chemin RX et bloc de contrôle et de puissance.

L'interface hôte est composée d'un total de 8 voies de SerDes à grande vitesse. Cela permet au module de prendre en charge une interfaces pour l'application 400G: une double interface client indépendante en mode 4 voies (pour l'application 400GbE) et quatre interfaces client indépendantes en mode double voie (pour l'application 4 * 100GbE).

L'interface de communication de gestion fournit un certain nombre d'opérations de gestion élémentaires qui permettent à l'hôte de lire ou d'écrire dans des registres de gestion de la taille d'un octet dans la carte de mémoire de gestion du module. Il existe des opérations de lecture et d'écriture à la fois pour les octets simples et pour les séquences d'octets contigus. Deux types d'opérations de lecture, soit avec adressage implicite (lu à partir de l'adresse actuelle), soit avec adressage explicite, sont pris en charge.

L'interface de communication de gestion distingue un rôle et un rôle de s. L'hôte est le et le module est le s.

Le initie toutes les opérations qui mènent au transfert de données. Les données peuvent être transférées du au s (dans les opérations d'écriture) et du s au (dans les opérations de lecture).

Caractéristiques

● Prend en charge l'espacement des canaux Flex-grid DWDM en bande C

● Interfaces côté client de soutien: 400GAUI-8/4*100GAUI-2

● Soutenir la DP-16QAM côté ligne avec CFEC

● Facteur de forme standard de type QSFP-DD 2

● Connecteur conforme MSA QSFP-DD 76pin

● Conforme aux 5.0 CMIS

● Conforme à l'accord de mise en œuvre de l'OIF pour le CMIS Cohérent, Rev 01.1

● OIF-400ZR-01.0_reduced2.pdf

● RoHS conforme

Application typique

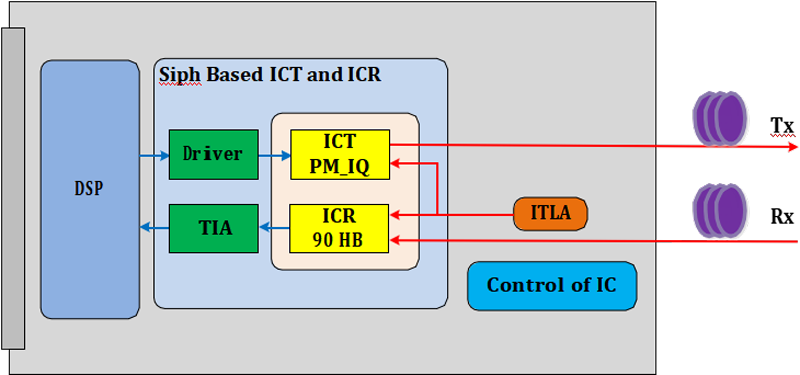

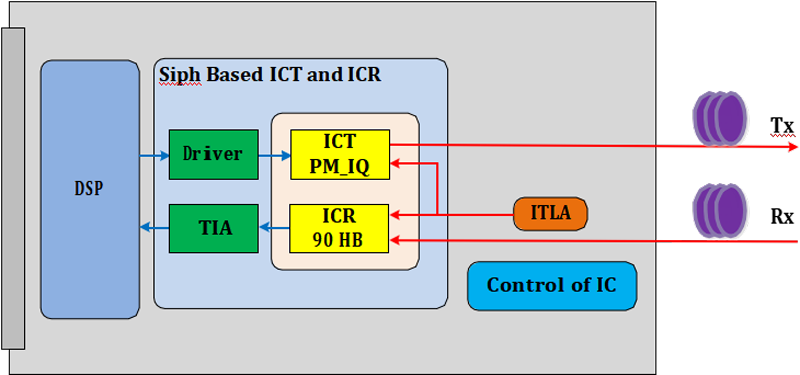

Le champ d'application du module est largement utilisé des interconnexions court-courrier (ZR) au métro (MR). Comme le montre la figure 1, il comprend des voies à haute donnée, une seule alimentation 3.3V, une interface IIC pour le contrôle du module et un rapport d'état, et les broches dédiées d'alarme et de contrôle (non indiquées sur la figure 1).

Figure 1. Diagramme du bloc émetteur-récepteur

Interface hôte

La prise en charge du module pour les applications larges avec les interfaces hôtes: 400GAUI-8/100GUI-2. L'interface hôte est conforme aux normes de protocole existantes et fonctionne sur des spécifications de couche physique standard. La terminaison, le mappage et/ou l'agrégation de ce signal est dans une structure de trame ZR interne. La structure du cadre ZR est ensuite adaptée au moteur CFEC et au cadre DSP pour la transmission sur l'interface média cohérente. La signalisation de l'interface hôte est conforme au protocole et aux normes électriques existants tels que définis par IEEE 802.3TM-2018.

L'interface hôte est conforme à une interface électrique puce à module à très courte portée CEI-56G VSR-PAM4 pour le codage PAM4.

Interface hôte | Taux de données d'application | Lane Count | Taux de signalisation de voie | Modulation |

400GAUI-8 | 425.00 Gb/s | 8 | 26.5625 GBaud ( /- 100 ppm) | PAM4 |

4*100GAUI-8 | 4*106.25 Gb/s | 8 | 26.5625 GBaud ( /- 100 ppm) | PAM4 |

Interface média

L'interface média utilise la modulation DP-16QAM, la détection cohérente de la diversité de polarisation et l'égalisation avancée de la liaison électronique avec dispersion omatique et compensation de retard de groupe différentiel.

Le module termine le signal d'interface hôte puis les mappe et les regroupe en une structure de trame ZR interne. La structure du cadre ZR est ensuite adaptée au moteur CFEC et au cadre DSP pour la transmission sur l'interface média cohérente.

Taux de bits d'application | Taux de bauds | Modulation | FEC |

478.75 Gb/s | 59.84375GBd | DP-16QAM | OFEC |

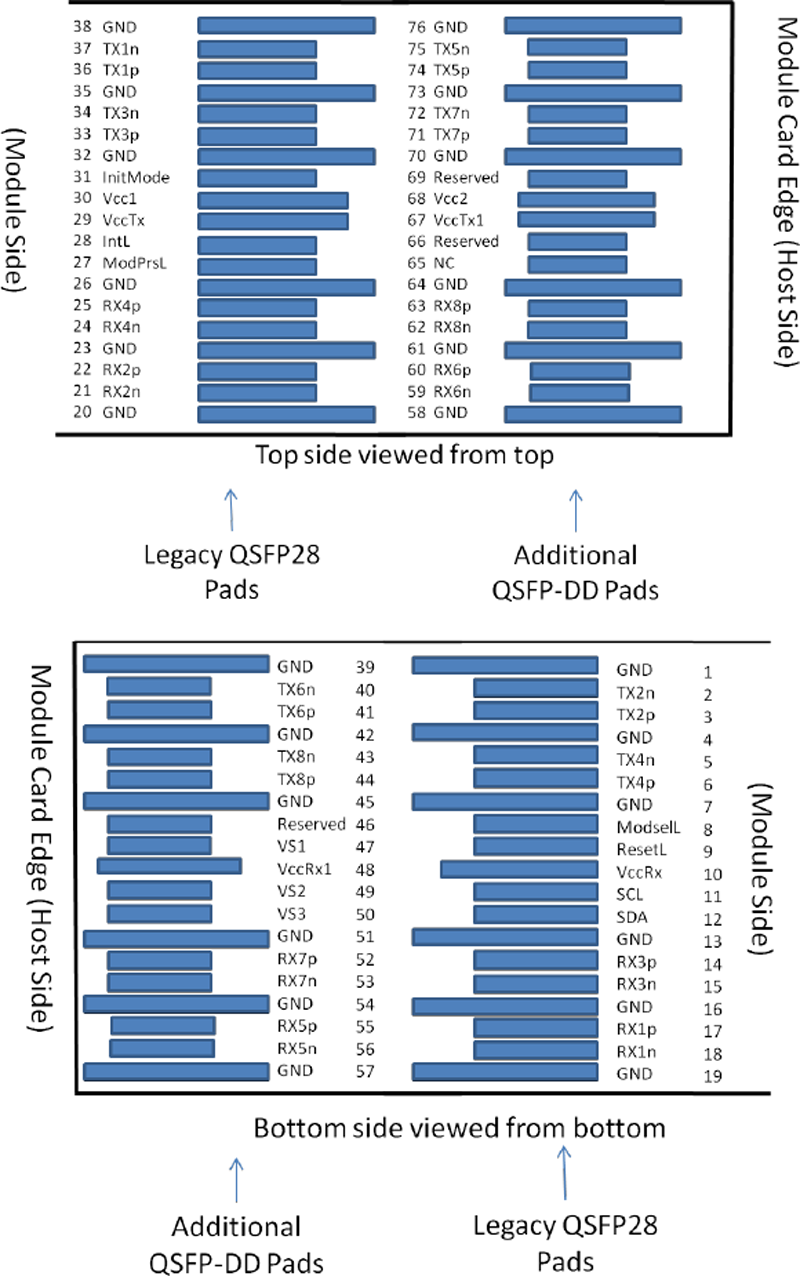

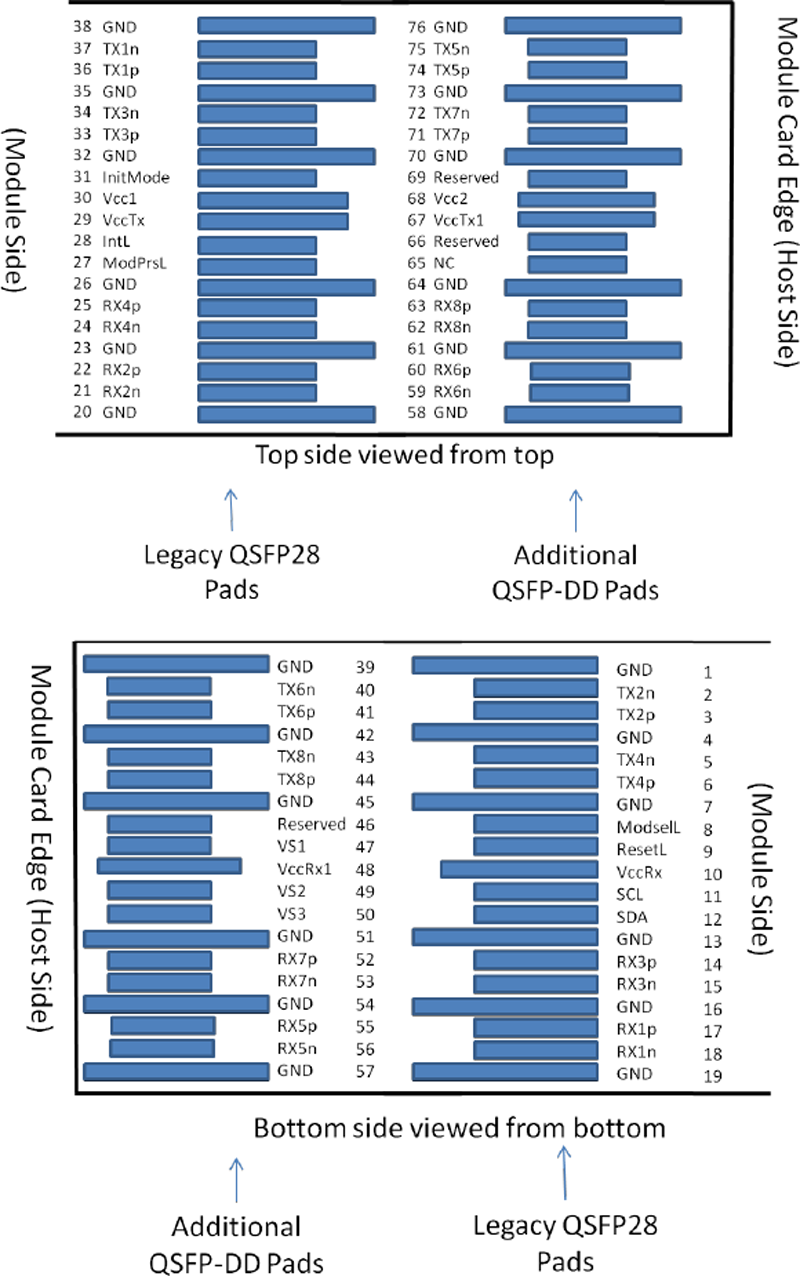

Connecteur électrique hôte et missions de broches

Les interfaces électriques, y compris les attributions de pads pour les données, le contrôle, l'état et les alimentations électriques et les exigences de disposition des PCB de l'hôte, du module sont entièrement conformes à la spécification QSFP-DD MSA QSFP-DD-Hardware, rev 5.0.

Le cas du module QSFP-DD est isolé de la terre de circuit du module, GND, pour fournir au concepteur d'équipement une flexibilité concernant les connexions entre les boucliers d'interférences électromagnétiques externes et la terre de circuit, GND, du module.

Figure 2. Connecteur conforme MSA

Épin # | Logique | Symbole | Deion | Plug Séquence |

1 |

| GND | Sol | 1B |

2 | CML-I | Tx2n | Entrée de données inversée par émetteur | 3B |

3 | CML-I | Tx2p | Entrée de données non inversée de l'émetteur | 3B |

4 |

| GND | Sol | 1B |

5 | CML-I | Tx4n | Entrée de données inversée par émetteur | 3B |

6 | CML-I | Tx4p | Entrée de données non inversée de l'émetteur | 3B |

7 |

| GND | Sol | 1B |

8 | LVTTL-I | ModSelL | Module Sélectionner | 3B |

9 | LVTTL-I | Réinitialiser | Réinitialisation du module | 3B |

10 |

| VccRx | Récepteur d'alimentation 3.3V | 2B |

11 | LVCMOS-I/O | SCL | Horloge d'interface série à 2 fils | 3B |

12 | LVCMOS-I/O | SDA | Données d'interface série à 2 fils | 3B |

13 |

| GND | Sol | 1B |

14 | CML-O | Rx3p | Sortie de données non inversée Récepteur | 3B |

15 | CML-O | Rx3n | Sortie de données inversée Récepteur | 3B |

16 | GND | Sol | 1B |

|

17 | CML-O | Rx1p | Sortie de données non inversée Récepteur | 3B |

18 | CML-O | Rx1n | Sortie de données inversée Récepteur | 3B |

19 |

| GND | Sol | 1B |

20 |

| GND | Sol | 1B |

21 | CML-O | Rx2n | Sortie de données inversée Récepteur | 3B |

22 | CML-O | Rx2p | Sortie de données non inversée Récepteur | 3B |

23 |

| GND | Sol | 1B |

24 | CML-O | Rx4n | Sortie de données inversée Récepteur | 3B |

25 | CML-O | Rx4p | Sortie de données non inversée Récepteur | 3B |

26 |

| GND | Sol | 1B |

27 | LVTTL-O | ModPrsL | Module présent | 3B |

28 | LVTTL-O | IntL | Interrompre | 3B |

29 |

| VccTx | Transmetteur d'alimentation 3.3V | 2B |

30 |

| Vcc1 | Alimentation électrique 3.3V | 2B |

31 | LVTTL-I | InitMode | Mode d'initialisation; Dans les applications QSFP héritées, le pavé InitMode est appelé LPMODE | 3B |

32 |

| GND | Sol | 1B |

33 | CML-I | Tx3p | Entrée de données non inversée de l'émetteur | 3B |

34 | CML-I | Tx3n | Entrée de données inversée par émetteur | 3B |

35 |

| GND | Sol | 1B |

36 | CML-I | Tx1p | Entrée de données non inversée de l'émetteur | 3B |

37 | CML-I | Tx1n | Entrée de données inversée par émetteur | 3B |

38 |

| GND | Sol | 1B |

39 |

| GND | Sol | 1A |

40 | CML-I | Tx6n | Entrée de données inversée par émetteur | 3A |

41 | CML-I | Tx6p | Entrée de données non inversée de l'émetteur | 3A |

42 |

| GND | Sol | 1A |

43 | CML-I | Tx8n | Entrée de données inversée par émetteur | 3A |

44 | CML-I | Tx8p | Entrée de données non inversée de l'émetteur | 3A |

45 |

| GND | Sol | 1A |

46 |

| Réservé | Pour une utilisation future | 3A |

47 |

| VS1 | Module fournisseur spécifique 1 | 3A |

48 |

| VccRx1 | Alimentation électrique 3.3V | 2A |

49 |

| VS2 | Module fournisseur spécifique 2 | 3A |

50 |

| VS3 | Module fournisseur spécifique 3 | 3A |

51 |

| GND | Sol | 1A |

52 | CML-O | Rx7p | Sortie de données non inversée Récepteur | 3A |

53 | CML-O | Rx7n | Sortie de données inversée Récepteur | 3A |

54 |

| GND | Sol | 1A |

55 | CML-O | Rx5p | Sortie de données non inversée Récepteur | 3A |

56 | CML-O | Rx5n | Sortie de données inversée Récepteur | 3A |

57 |

| GND | Sol | 1A |

58 |

| GND | Sol | 1A |

59 | CML-O | Rx6n | Sortie de données inversée Récepteur | 3A |

60 | CML-O | Rx6p | Sortie de données non inversée Récepteur | 3A |

61 |

| GND | Sol | 1A |

62 | CML-O | Rx8n | Sortie de données inversée Récepteur | 3A |

63 | CML-O | Rx8p | Sortie de données non inversée Récepteur | 3A |

64 |

| GND | Sol | 1A |

65 |

| NC | Pas de connexion | 3A |

66 |

| Réservé | Pour une utilisation future | 3A |

67 |

| VccTx1 | Alimentation électrique 3.3V | 2A |

68 |

| Vcc2 | Alimentation électrique 3.3V | 2A |

69 |

| Réservé | Pour une utilisation future | 3A |

70 |

| GND | Sol | 1A |

71 | CML-I | Tx7p | Entrée de données non inversée de l'émetteur | 3A |

72 | CML-I | Tx7n | Entrée de données inversée par émetteur | 3A |

73 |

| GND | Sol | 1A |

74 | CML-I | Tx5p | Entrée de données non inversée de l'émetteur | 3A |

75 | CML-I | Tx5n | Entrée de données inversée par émetteur | 3A |

76 |

| GND | Sol | 1A |

Évaluations maximales absolues

Il faut noter que le fonctionnement au-delà de toute valeur nominale maximale absolue individuelle pourrait causer des dommages permanents à ce module.

Paramètre | Min | Max | Unités | Notes |

Température de stockage | -40 | 85 | ℃ |

|

Humidité de stockage (relative) | - | 85 | % | Non-condensation |

Température du cas | 0 | 75 | ℃ |

|

Humidité de fonctionnement (relative) | - | 85 | % | Non-condensation |

Température du boîtier de fonctionnement à court terme |

| 80 | ℃ | <24 heures |

Gamme absolue d'alimentation | -0.3 | 3.63 | V |

|

Puissance d'entrée maximale optique RX | - | 10 | DBm |

|

Conditions de fonctionnement

Paramètre | Min | Max | Unités | Notes |

Température du boîtier de fonctionnement | 0 | 75 | ℃ |

|

Humidité de fonctionnement (relative) | - | 85 | % | Non-condensation |

Plage de fonctionnement de l'alimentation | 3.135 | 3.465 | V |

|

Puissance d'entrée optique RX | - | 0 | DBm |

|

Alimentation électrique

Le 400G ZR QSFP-DD DCO est un module Power Class 8. Afin d'éviter de dépasser la capacité d'alimentation du système hôte, lors de la prise à chaud, du cycle d'alimentation ou de la réinitialisation, tous les modules QSFP-DD doivent être mis sous tension en mode faible puissance si le mode LPMode est affirmé. Si LPMode n'est pas affirmé, le module passera en mode haute puissance sans intervention de l'hôte. Les valeurs de spécification des courants maximums instantanés, soutenus et stationnaires à chaque classe de puissance sont données dans le tableau 5. Les exigences d'alimentation sont spécifiées dans le tableau ci-dessous.

Paramètre | Min | Typique | Max | Unités | Notes |

3.3V DC Puissance Tension d'alimentation | 3.135 | 3.3 | 3.465 | V |

|

3.3V DC Puissance Courant d'approvisionnement |

|

| 7 | A |

|

Dissipation de puissance |

|

| 18 | W |

|

Consommation de puissance faible |

|

| 1.5 | W |

|

Module Inrush Courant |

|

| 100 | MA/us |

|

Courant de mise hors tension

| -100 |

|

| MA/us |

|

Bruit d'alimentation |

|

| 25 | MV |

|

Pins de contrôle matériel et d'état

En plus de l'interface série à 2 fils, le module dispose des signaux à basse vitesse suivants pour le contrôle et l'état:

● ModSelL

● Réinitialiser

● LPMode

● ModPrsL

● IntL

● Epps

ModSelL

Le ModSelL est un signal d'entrée qui doit être tiré sur Vcc dans le module QSFP-DD. Lorsqu'il est maintenu bas par l'hôte, le module répond aux commandes de communication série à 2 fils. Le ModSelL permet l'utilisation de plusieurs modules QSFP-DD sur un seul bus d'interface à 2 fils. Lorsque ModSelL est «élevé», le module ne doit pas répondre ou n'accepter aucune communication d'interface à 2 fils de l'hôte.

Afin d'éviter les conflits, le système hôte ne doit pas tenter de communications d'interface à 2 fils dans le temps de désaffirmation de ModSelL après l'acte de QSFP-DD modules. De même, l'hôte doit attendre au moins la période du temps d'affirmation de ModSelL avant de communiquer avec le module nouvellement ed. Les périodes d'assertion et de désassertion de différents modules peuvent se chevaucher tant que les exigences de synchronisation ci-dessus sont remplies.

Réinitialiser

Le signal ResetL doit être tiré sur Vcc dans le module. Un niveau bas sur le signal ResetL pour une durée supérieure à la longueur d'impulsion minimale (t_Reset_init) initie une réinitialisation complète du module, renvoyant tous les paramètres du module utilisateur à leur état par défaut.

LPMode

LPMode est un signal d'entrée. Le signal LPMode doit être tiré jusqu'à Vcc dans le module QSFP-DD. LPMode est utilisé dans le contrôle du mode d'alimentation du module.

Voir la section 6.3.1.3 du SMIC.

ModPrsL

ModPrsL doit être tiré vers le haut jusqu'à Vcc Host sur la carte hôte et tiré bas dans le module. Le ModPrsL est affirmé «Low» lorsque le module est ed. Le ModPrsL est dégradé «High» lorsque le module est physiquement absent du connecteur hôte en raison de la résistance de traction sur la carte hôte.

La signalisation basse vitesse autre que l'interface SCL et SDA est basée sur le TTL basse tension (LVTTL) fonctionnant en Vcc. Vcc fait référence aux tensions d'alimentation génériques de VccTx, VccRx, Vcc host ou Vcc1. Les hôtes doivent utiliser une résistance de traction connectée à l'hôte Vcc sur chacune des interfaces à 2 fils SCL (horloge), SDA (données) et toutes les sorties d'état à faible vitesse. Le SCL et SDA est une interface hot plug qui peut prendre en charge une topologie de bus. Pendant l'ion du module ou le retrait, le module peut mettre en œuvre un circuit pré-ge qui empêche de corrompre les transferts de données d'autres modules qui utilisent déjà le bus.

Les spécifications électriques à faible vitesse QSFP-DD sont données dans le tableau 6. Cette spécification garantit la compatibilité entre le bus hôte et l'interface à 2 fils.

Paramètre | Symbole | Min | Max | Unité | Condition |

SCL et SDA | VOL | 0 | 0.4 | V | IOL(max)= 3 mA pour le mode rapide, 20 mA pour le mode rapide plus |

SCL et SDA | VIL | -0.3 | Vcc * 0.3 | V |

|

VIH | Vcc * 0.7 | 0.5 Vcc | V |

|

Capacité pour SCL et SDA Signal d'E/S | Ci |

| 14 | PF |

|

Total bus Charge capacitive Pour SCL et SDA | Cb |

| 100 | PF | Pour la fréquence d'horloge de 400 kHz, utilisez la résistance de traction de 3.0k Ohms, max. |

|

| 200 | PF | Pour la fréquence d'horloge de 400 kHz, utilisez la résistance de traction de 1.6k Ohms, max. |

LPMode, Réinitialiser, ModSelL Et EPPS | VIL | -0.3 | 0.8 | V |

|

VIH | 2 | 0.3 Vcc | V |

|

LPMode, Réinitialiser Et ModSelL | | Iin | |

| 360 | UA | 0V |

EPPS | | Iin | |

| À déterminer | UA | 0V |

IntL | VOL | 0 | 0.4 | V | IOL = 2.0 mA |

VOH | Vcc - 0.5 | 0.3 Vcc | V | 10k Ohms pull-up pour Hôte Vcc |

ModPrsL | VOL | 0 | 0.4 | V | IOL = 2.0 mA |

VOH |

|

| V | ModPrsL peut être implémenté en tant que court-circuit vers GND sur le module |

Couche physique

La couche physique supportant la communication entre l'hôte et le module est l'interface série Two Wire (TWI). Le TWI se compose d'un signal d'horloge (SCL) et d'un signal de données (SDA).

SCL et SDA comprennent une interface série à 2 fils entre l'hôte et le module utilisant le protocole TWI. SCL est défini comme le signal d'horloge d'interface série et SDA comme signal de données d'interface série. Les deux signaux sont à drain ouvert et nécessitent des résistances de traction à 3.3V sur l'hôte. La valeur de la résistance de traction doit être de 1k ohms à 4.7k ohms en fonction de la charge capacitive.

Les deux signaux (SCL et SDA) sont des broches à collecteur ouvert bidirectionnel et nécessitent une traction externe vers VCC sur le PCB hôte. L'activation de la ligne nécessite de la tirer vers le bas (câblée). La capacité totale du bus ne doit pas dépasser 400pF.

Cette interface à 2 fils prend en charge les vitesses de bus:

· Mode rapide-Mode rapide I2C (Fm) ≤ 400 kbit/s

· Mode rapide plus - I2C Rapide-Mode Plus (Fm +) ≤ 1 Mbit/s

Le signal SDA est bidirectionnel. Pendant le transfert de données binaires, le signal SDA doit faire la transition lorsque SCL est faible. Les transitions SDA lorsque SCL est élevé sont utilisées pour marquer le début (START) ou la fin (STOP) d'un transfert de données.

Spécifications électriques à grande vitesse

L'émetteur et le récepteur sont conformes à la spécification électrique CEI-56G-VSR-PAM4 (OIF-CEI-04.0).

Les lignes de données sont couplées AC et terminées dans le module selon le chiffre suivant du QSFP-DD MSA. Les signaux à grande vitesse suivent les spécifications électriques des CEI-56G-VSR-PAM telles que définies en OIF-CEI-04.0.

Les signaux à grande vitesse se composent de 8 paires différentielles d'émission et 8 de réception identifiées comme TX[8:1]p / TX[8:1]n et RX[8:1]p / RX[8:1]n. Ces signaux peuvent être utilisés en 400GAUI-8 en fonction de la capacité du mode host.400GAUI-8 fournit 8 voies différentielles en utilisant la signalisation PAM4 fonctionnant à 26.5625 GBaud. Il en résulte 8 voies de 50 Gb/s pour un total de 400 Gb/s. Ce mode permet la connexion aux configurations PMD de 400GUAI-8.

Les actériques électriques suivantes sont définies par rapport à l'environnement d'exploitation recommandé, sauf indication contraire.

Caractéristiques électriques pour l'émetteur

Paramètre | Min | Typique | Max | Unités | Notes |

Taux de signal, Chaque Lane | 26.5625 ± 100ppm | GBaud |

|

Différentiel Entrée de crête-crête Tolérance de tension |

|

| 900 | MVpp |

|

Caractéristiques électriques pour le récepteur

Paramètre | Min | Typique | Max | Unités | Notes |

Taux de signal, Chaque Lane | 26.5625 ± 100ppm | GBaud |

|

Différentiel Entrée de crête-crête Tolérance de tension |

| 750 | 900 | MVpp |

|

Temps de transition, 20% à 80% |

| 9.5 |

| Ps |

|

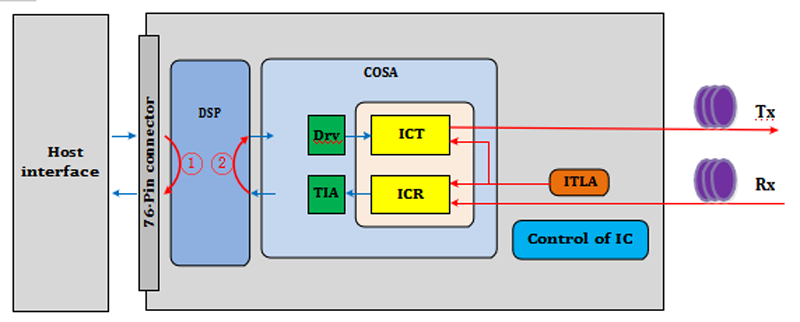

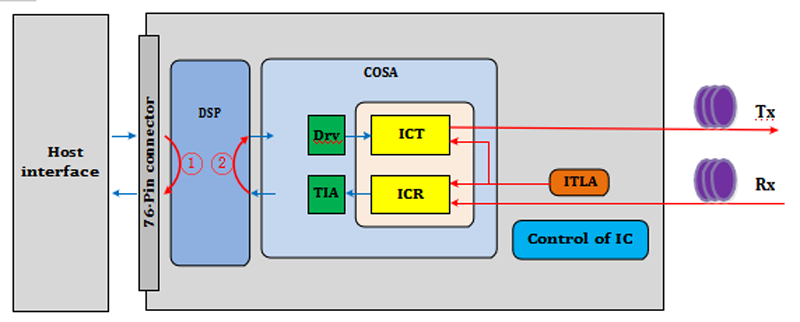

Recul

Le module prend en charge la fonctionnalité de bouclage. Le bouclage de l'hôte (Loopback ①) et le bouclage du réseau (Loopback ②) sont affichés à la figure 4. Pour plus de détails sur le contrôle du mode de bouclage, veuillez vous référer à Référence [2]. En boucle optionnelle, TXn est retourné à RXn, par exemple TX0 vers RX0, à la fois côté hôte et média.

Figure3:Module Orientation de la boucle

Spécifications optiques

Toutes les spécifications données dans ce document sont des numéros de fin de vie et sont valables dans des conditions d'exploitation sauf indication spécifique:

Spécifications de l'émetteur optique

Paramètre | Min | Typ. | Max | Unité | Notes |

Émetteur Fréquence Gamme | 191.3 | 193.7 | 196.1 | THz | Bande C 75GHz ITU-T grille. Plage de fréquence sur laquelle les spécifications sont maintenées, sauf indication contraire. |

Stabilité de fréquence laser | -1.8 |

| 1.8 | GHz | Stabilité de fréquence par rapport à la grille de l'UIT. |

Précision de fréquence laser | -1.8 |

| 1.8 | GHz |

|

Fréquence laser Gamme de réglage fin | -6.0 |

| 6.0 | GHz |

|

Résolution de réglage fine |

| 100 |

| MHz |

|

Vitesse d'accordage sous la Manche | - |

| 60 | S |

|

Largeur de ligne laser |

|

| 100 | KHz |

|

Sortie de l'émetteur Gamme de puissance |

| -9.5 |

| DBm |

|

Émetteur Laser Désactiver le temps |

|

| 180 | Ms |

|

Stabilité de puissance de sortie | -0.5 |

| 0.5 | DB | Différence sur la température, le temps, la longueur d'onde et le vieillissement. |

Précision de puissance de sortie | -2 |

| 2 | DB | Différence entre la valeur définie et Valeur réelle par rapport au vieillissement. |

Émetteur Heure de la mise en marche À partir de Cold Start | - |

| 120 | S |

|

Émetteur OSNR (Inband) | 34 |

| - | DB/0.1nm |

|

Émetteur Réflectance arrière | - |

| -24 | DB |

|

Puissance de sortie de l'émetteur Avec TX Désactivé | - |

| -20 | DBm |

|

Polarisation de l'émetteur Puissance dépendante | - |

| 1.5 | DB | Dérférence de puissance entre la polarisation X et Y |

Récepteur optique Spécifications

Paramètre | Min | Typ. | Max | Unité | Notes |

Gamme de fréquence du récepteur | 191.3 | 193.7 | 196.1 | THz |

|

Gamme de puissance d'entrée | -12 |

| 0 | DBm | Puissance du signal du canal à la pénalité OSNR <0.5dB |

Sensibilité d'OSNR |

| 24 | 26 | DB/0.1nm |

|

Sensibilité du récepteur |

|

| -20 | DBm | Puissance d'entrée nécessaire pour atteindre la post FEC BER < 1E-15 lorsque la tolérance OSNR> 26dB/0.1nm |

Los Assert | -24 |

| -20 | DBm |

|

Los Hystérésis | 1.0 |

| 2.5 | DB |

|

Tolérance CD | 2400 |

|

| Ps/nm | Tolérance à la dispersion chromatique. |

Tolérance PMD | 10 |

|

| Ps | Tolérance à la PMD avec une pénalité <0.5 dB à la sensibilité OSNR. |

Tolérance PDL de crête | 3.5 |

|

| DB | La tolérance au PDL maximal avec une pénalité <1.3 dB à la sensibilité OSNR lorsque le changement de SOP est <= 1 rad/ms. |

Tolérance à Changement dans les SOP | 50 |

| - | Rad/ms |

|

Puissance d'entrée Tolérance transitoire | -2 |

| 2 | DB | Tolérance au changement de puissance d'entrée avec une pénalité <0.5 dB à la sensibilité OSNR. |

Puissance d'entrée Précision de lecture | -2 |

| 2 | DB |

|

Perte de retour optique | -20 |

|

| DB | Réflectance optique à l'entrée du connecteur Rx. |

Récepteur Turn-up Temps À partir de Cold Start | - |

| 120 | S | À partir de la réinitialisation du module, avec un signal d'entrée optique valide présent. |

Force d'insertion, d'extraction et de rétention

Paramètre | Min | Max | Unité | Note |

Force d'insertion |

| 90 | N |

|

Force d'extraction |

| 50 | N |

|

Force de rétention | 90 |

| N |

|

Spécification EMI, EMC et ESD

Le module est conforme aux exigences énumérées dans le tableau ci-dessous lorsqu'il est installé dans l'équipement hôte.

Paramètre | Référence | Valeur | Unité | Notes |

Immunité ESD | IEC 61000-4-2 | 8 | KV | Disge de contact |

15 | KV | Disge d'air |

ESD (modèle HBM) | JEDEC JESD22-A114-B | 1 | KV | Contacts à grande vitesse |

2 | KV | Autres épingles |

Immunité EMC | IEC 61000-4-3 |

|

|

|

Emission d'EMI | FCC Classe B |

|

|

|

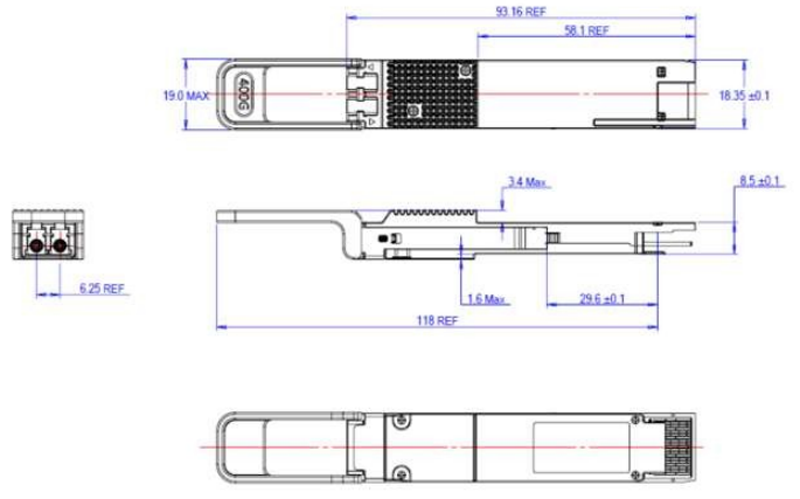

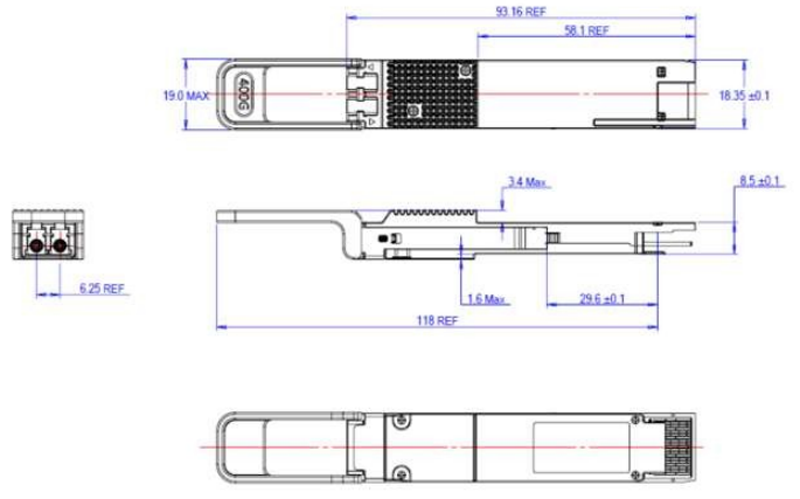

Dessin de contour (mm)

Figure4: Module QSFP-DD Dessin mécanique

Centre de données Internet

Centre de données Internet FAQ

FAQ Nouvelles de l'industrie

Nouvelles de l'industrie À propos de nous

À propos de nous Commutateur de centre de données

Commutateur de centre de données  Commutateur d'entreprise

Commutateur d'entreprise  Interrupteur industriel

Interrupteur industriel  Interrupteur d'accès

Interrupteur d'accès  Réseau intégré

Réseau intégré  Module optique et câble

Module optique et câble

Appelez-nous sur:

Appelez-nous sur:  Nous envoyer un courriel:

Nous envoyer un courriel:  2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.