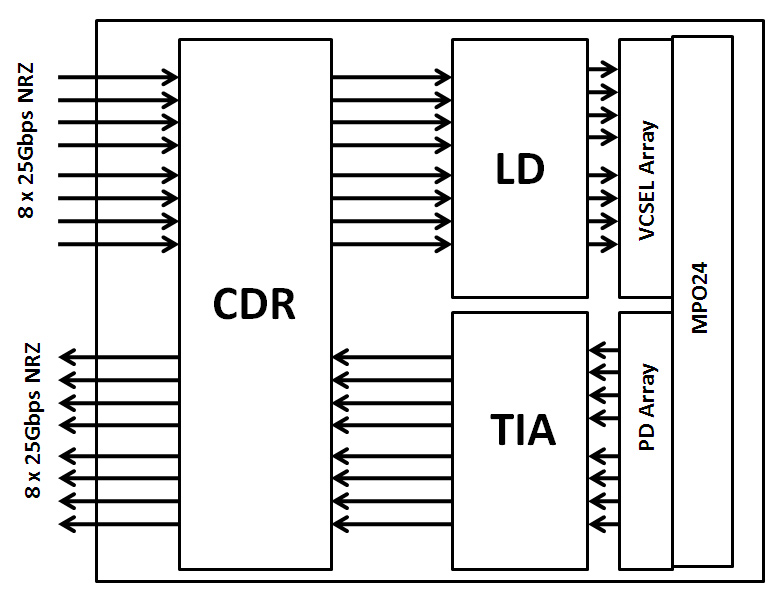

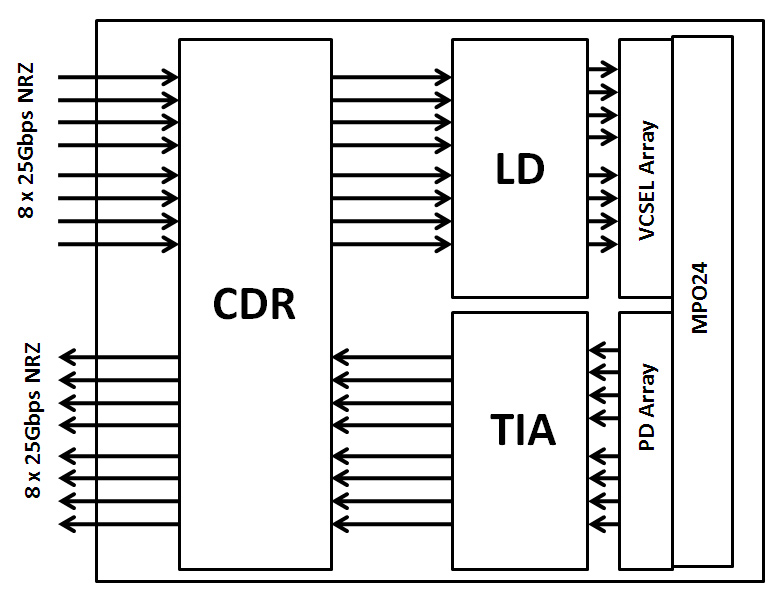

L'émetteur-récepteur 2x100GBASE-SR4 QSFPDD est un type d'émetteur-récepteur parallèle, le paquet de tableaux VCSEL et PIN est la technique clé, via le système I2C peut entrer en contact avec le module. Il s'agit d'une double densité de QSFP à huit canaux, enfichables, parallèles et optiques, pour les applications Ethernet Gigabit 2x100, module haute performance pour les applications de communication de données à voies multiples à courte portée et d'interconnexion. Il intègre huit voies de données dans chaque direction avec une bande passante de 8x25.78125Gbps. Chaque voie peut fonctionner à 25.78125Gbps jusqu'à 70 m en utilisant la fibre OM3 ou 100 m en utilisant la fibre OM4. Ces modules sont conçus pour fonctionner sur des systèmes de fibre multimode en utilisant une longueur d'onde nominale de 850nm. L'interface électrique utilise un connecteur de type bord de contact 76. L'interface optique utilise un connecteur MTP (MPO) à 24 fibres. Ce module intègre des circuits éprouvés et la technologie VCSEL pour fournir une longue durée de vie fiable, des performances élevées et un service cohérent.

Figure 1. Diagramme de bloc de module

Caractéristiques

● Modules d'émetteur-récepteur duplex intégral à 8 canaux

● Débit de données de transmission jusqu'à 26Gbps par canal

● Réseau VCSEL 8 canaux 850nm

● Réseau de détecteurs de photos PIN à 8 canaux

● Circuits CDR internes sur les canaux récepteur et émetteur

● Contournement CDR de soutien

● Consommation de puissance faible <4W

● Facteur de forme QSFP DD à chaud

● Longueur de liaison maximale de 70m sur OM3 Fibre multimode (MMF) et 100m sur OM4 MMF

● Connecteur MPO24 réceptacle

● Température du boîtier de fonctionnement 0 °C à 70 °C

● Tension d'alimentation 3.3V

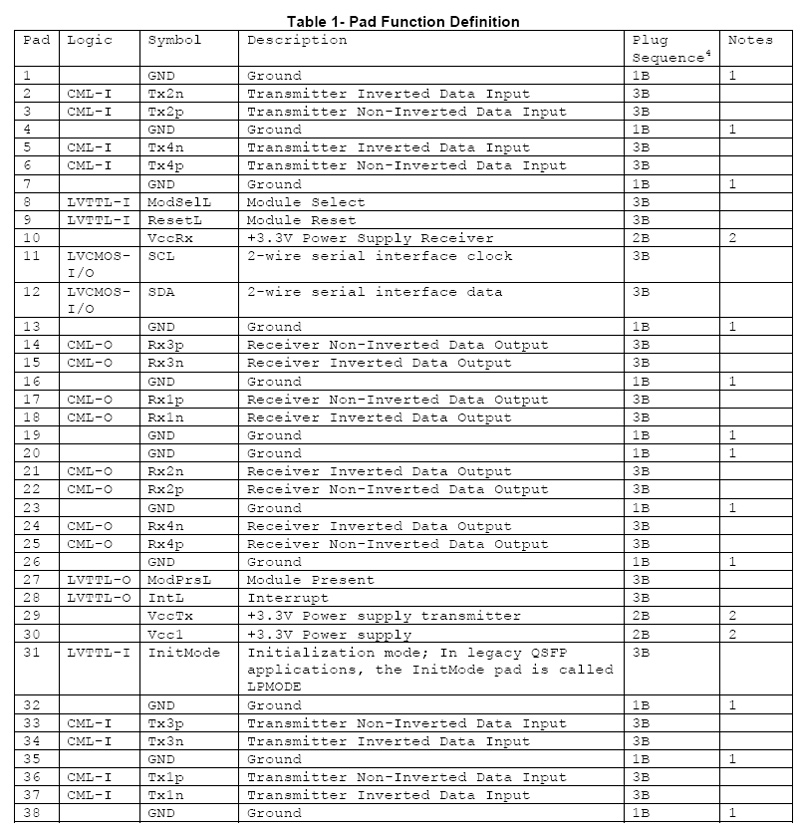

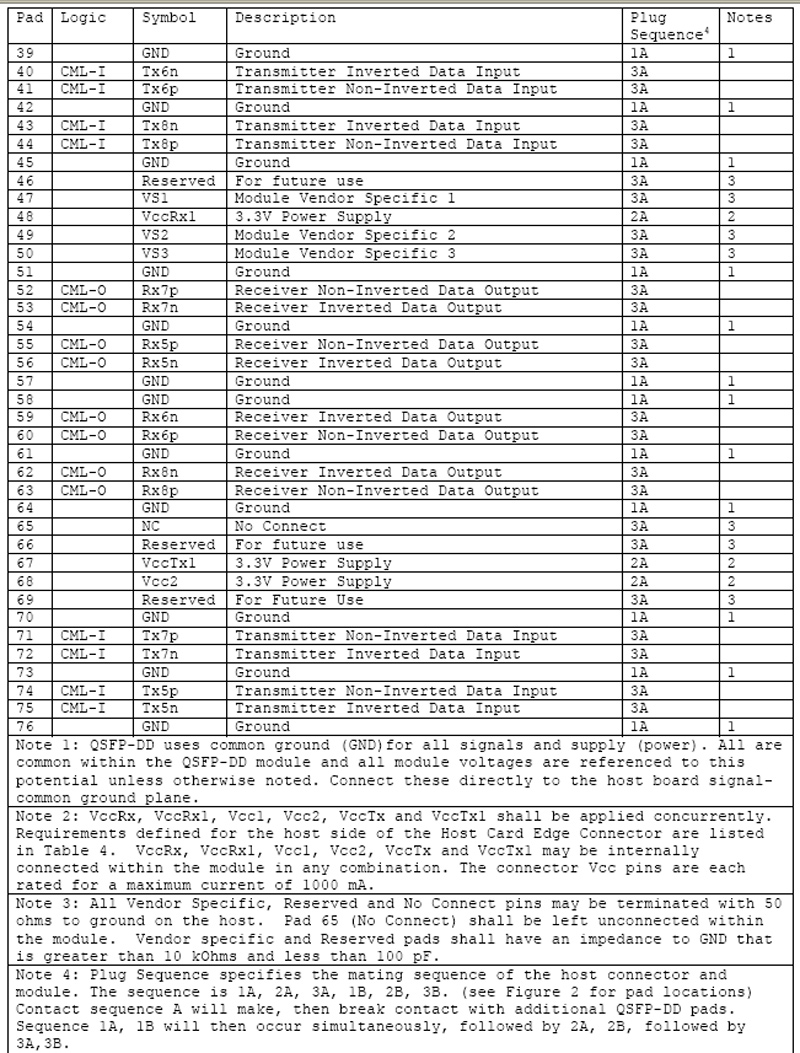

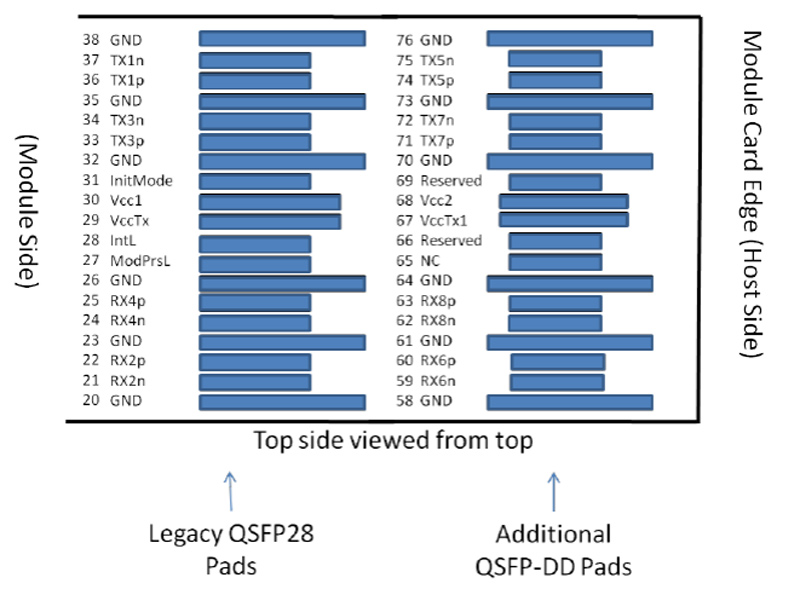

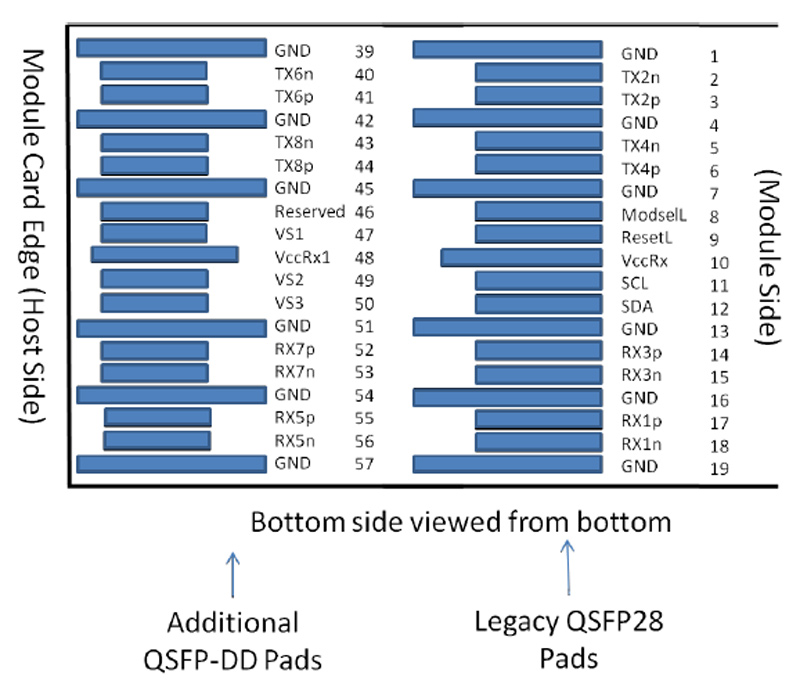

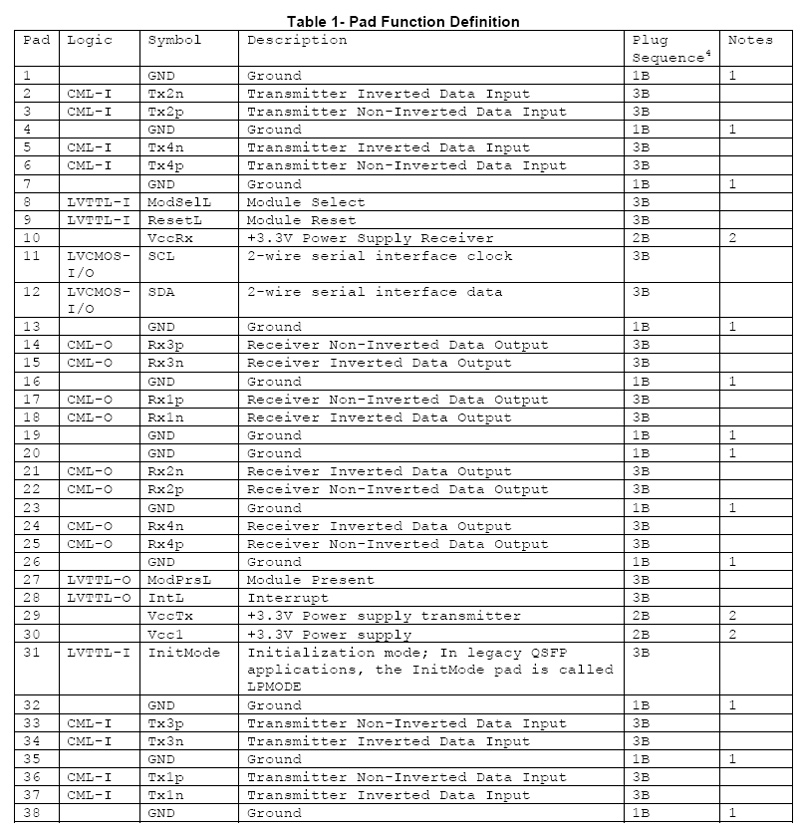

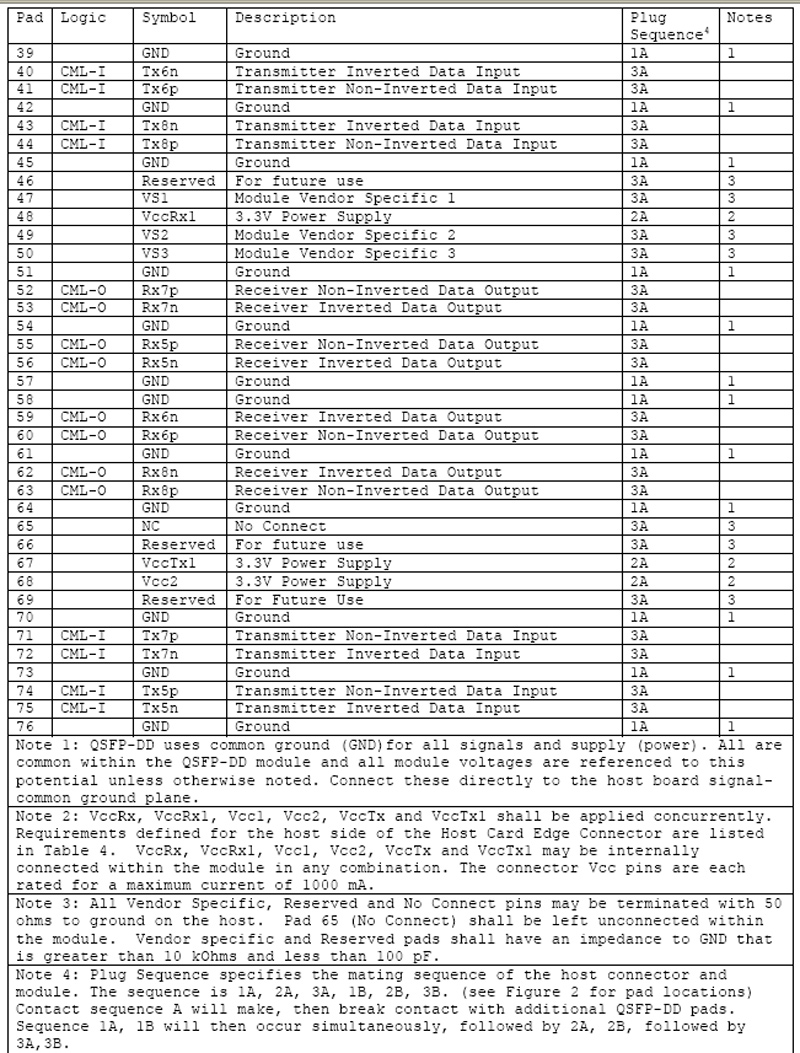

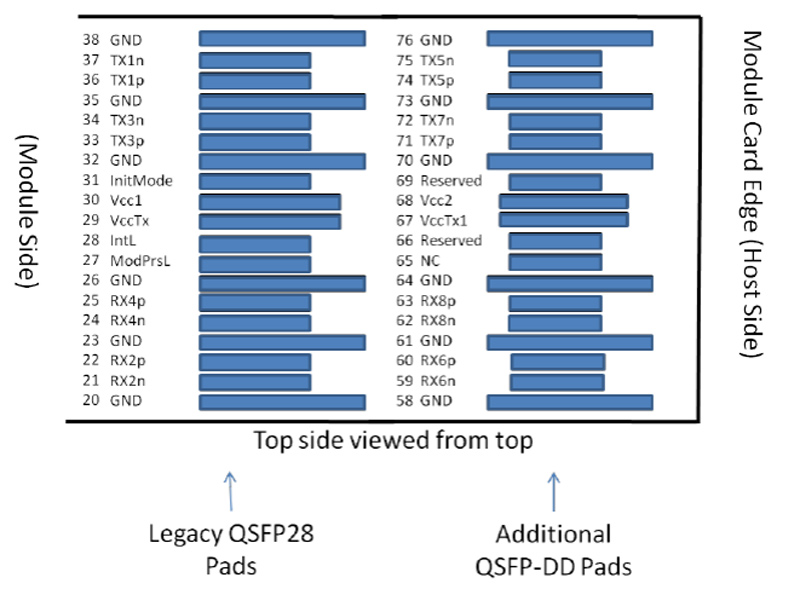

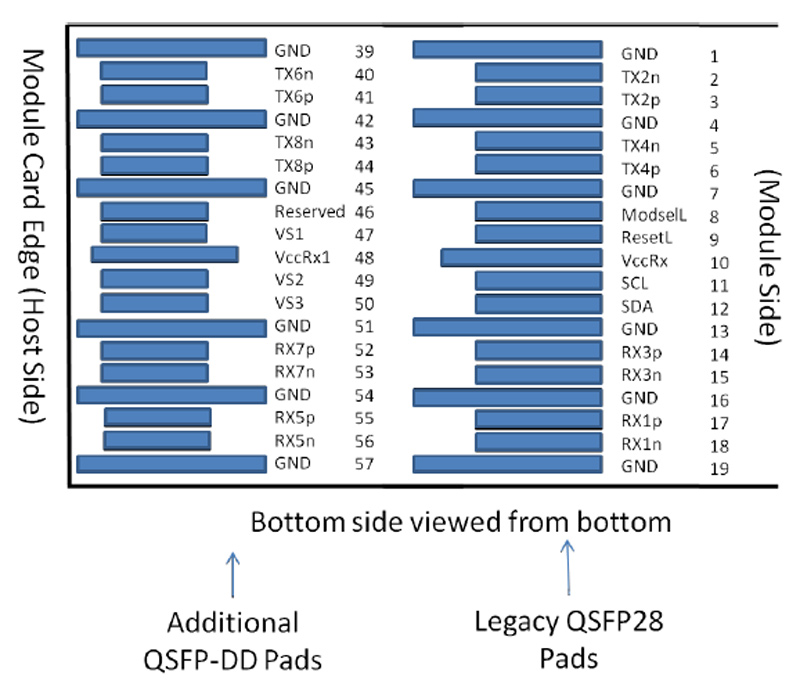

Pin Deion

Figure 2. Détails de la sortie électrique

Pin ModSelL

Le ModSelL est un signal d'entrée qui doit être tiré vers Vcc dans le module QSFP-DD. Lorsqu'il est maintenu bas par l'hôte, le module répond aux commandes de communication série à 2 fils. Le ModSelL permet l'utilisation de plusieurs modules QSFP-DD sur un seul bus d'interface à 2 fils. Lorsque ModSelL est «élevé», le module ne doit pas répondre ou n'accepter aucune communication d'interface à 2 fils de l'hôte.

Afin d'éviter les conflits, le système hôte ne doit pas tenter de communications d'interface à 2 fils dans le temps de désaffirmation de ModSelL après l'acte de QSFP-DD modules. De même, l'hôte doit attendre au moins la période du temps d'affirmation de ModSelL avant de communiquer avec le module nouvellement ed. Les périodes d'assertion et de désassertion de différents modules peuvent se chevaucher tant que les exigences de synchronisation ci-dessus sont remplies.

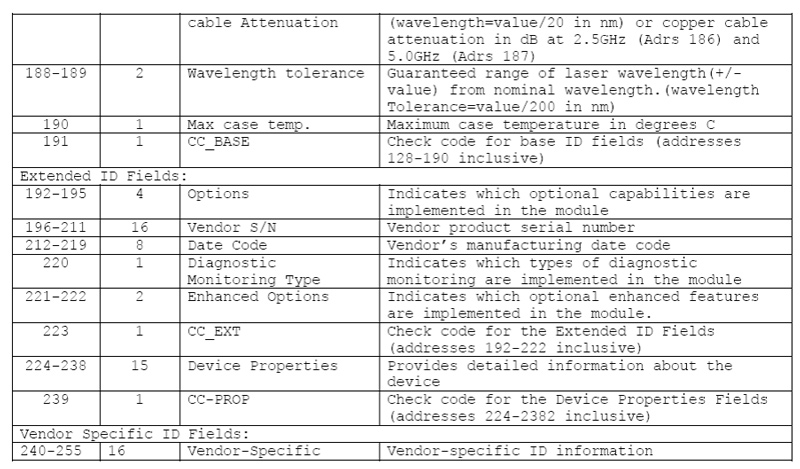

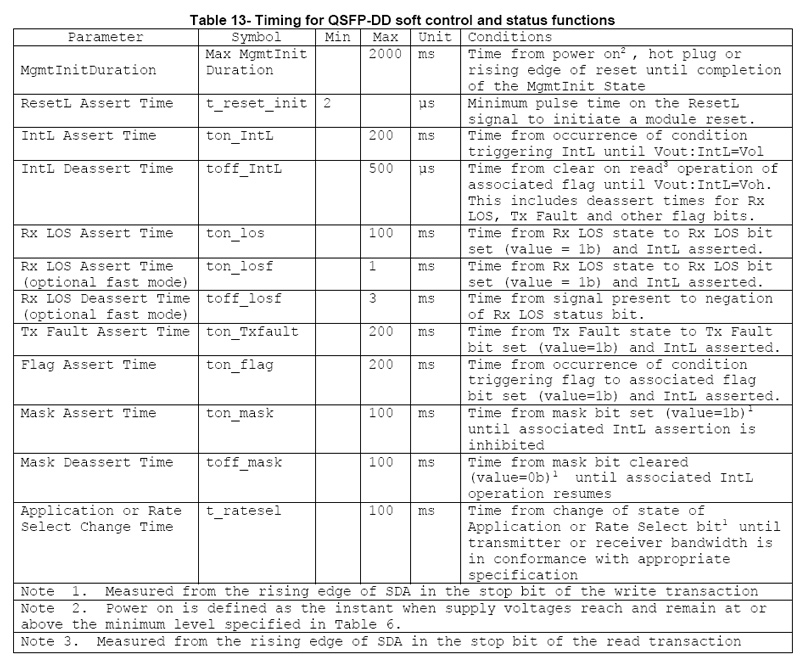

Étui de réinitialisation

Le signal ResetL doit être tiré sur Vcc dans le module. Un niveau bas sur le signal ResetL pour une durée supérieure à la longueur d'impulsion minimale (t_Reset_init) (voir tableau 13) initie une réinitialisation complète du module, renvoyant tous les paramètres du module utilisateur à leur état par défaut.

InitMode Pin

InitMode est un signal d'entrée. Le signal InitMode doit être tiré jusqu'à Vcc dans le module QSFP-DD. Le signal InitMode permet à l'hôte de définir si le module QSFP-DD s'initialisera sous le contrôle logiciel hôte (IniMode affirmé High) ou le contrôle matériel du module (InitMode dégradé Low). Sous le contrôle du logiciel hôte, le module doit rester en mode faible consommation jusqu'à ce que le logiciel permette la transition vers le mode haute puissance, tel que défini dans la section 7.5. Sous le contrôle matériel (InitMode dé-affirmé Low), le module peut immédiatement passer en mode haute puissance après l'initialisation de l'interface de gestion. L'hôte ne changera pas l'état de ce signal pendant que le module est présent. Dans les applications QSFP héritées, ce signal est nommé LPMode. Voir SFF-8679 pour le signal deion.

Pin ModPrsL

ModPrsL doit être tiré vers le haut vers Vcc Host sur la carte hôte et mis à la terre dans le module. Le ModPrsL est affirmé «Low» lorsque le module est ed et dégradé «High» lorsque le module est physiquement absent du connecteur hôte.

Étui intL

IntL est un signal de sortie. Le signal IntL est une sortie collecteur ouverte et doit être tiré sur Vcc Host sur la carte hôte. Lorsque le signal IntL est affirmé Low, il indique un changement d'état du module, un défaut opérationnel possible du module ou un état critique pour le système hôte. L'hôte identifie la source de l'interruption à l'aide de l'interface série à 2 fils. Le signal IntL est dégradé «High» après la lecture de tous les drapeaux d'interruption réglés.

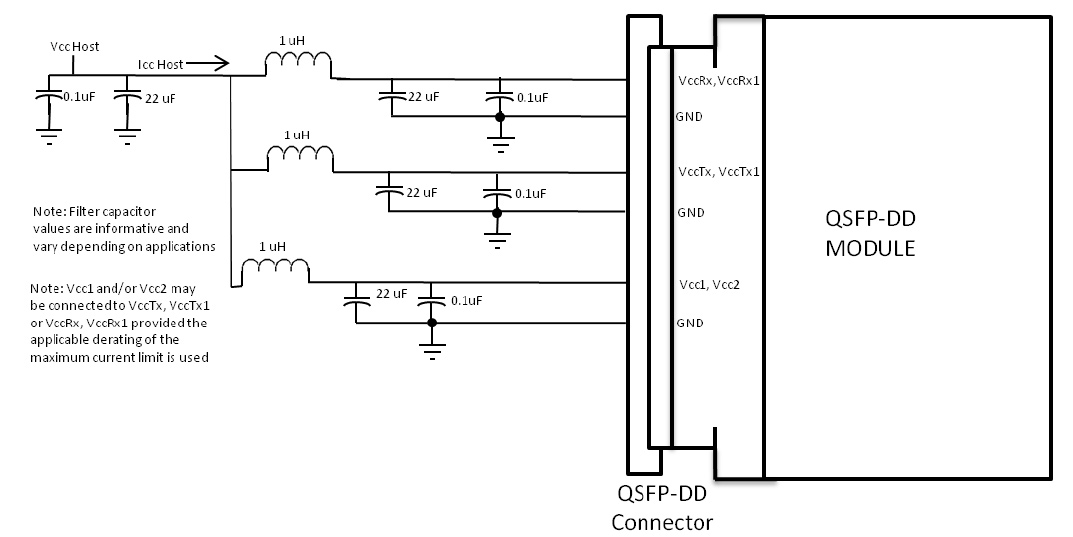

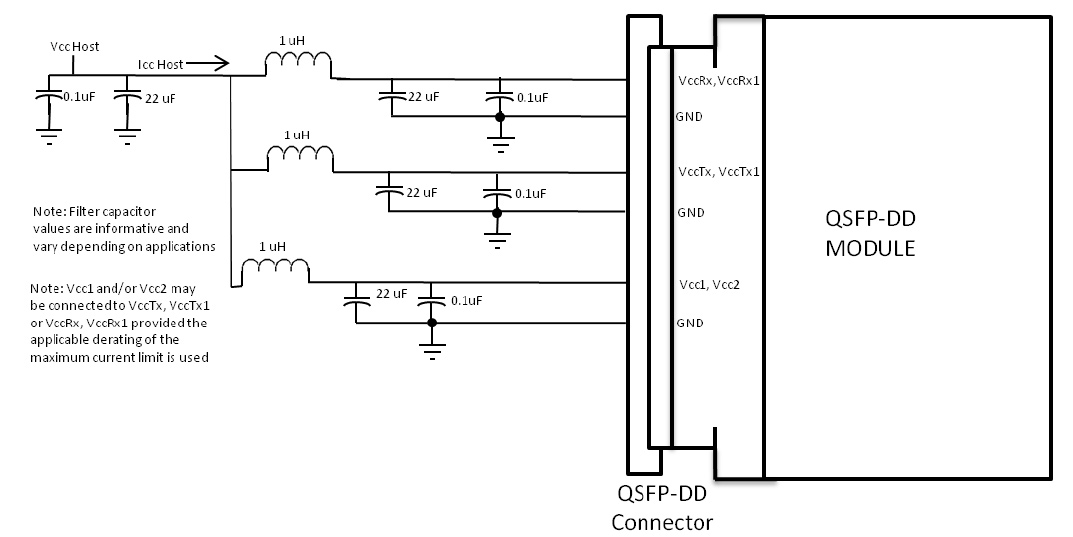

Filtrage de l'alimentation électrique

La carte hôte doit utiliser le filtrage d'alimentation indiqué sur Figure3.

Figure 3. Filtrage d'alimentation de la carte hôte

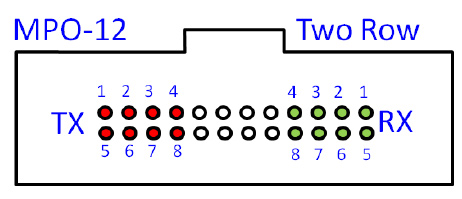

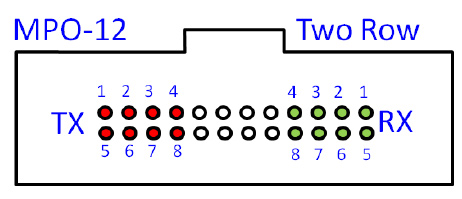

Voies d'interface optique et affectation

Le port d'interface optique est un connecteur mâle MPO24.

Figure 4. Réceptacle optique et orientation des canaux

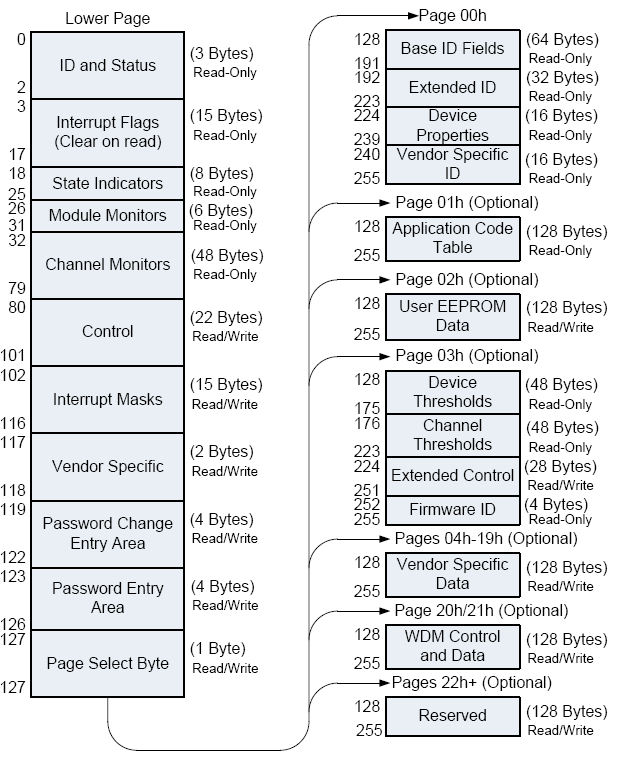

INTERFACE DE SURVEILLANCE DIAGNOSTIQUE (FACULTATIF)

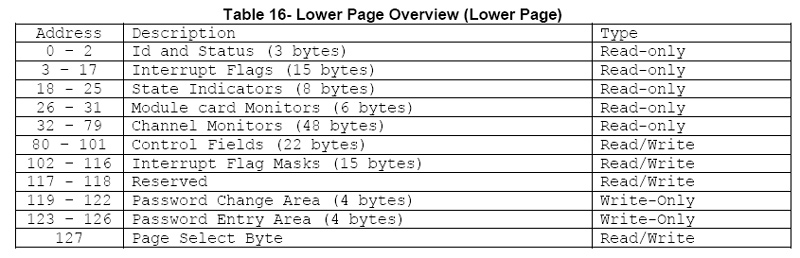

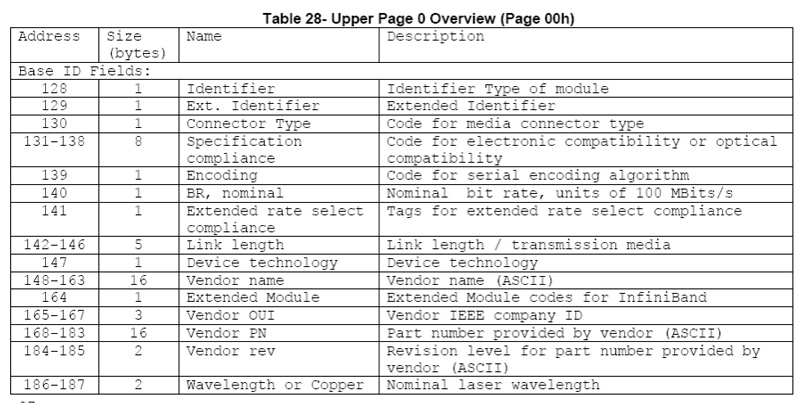

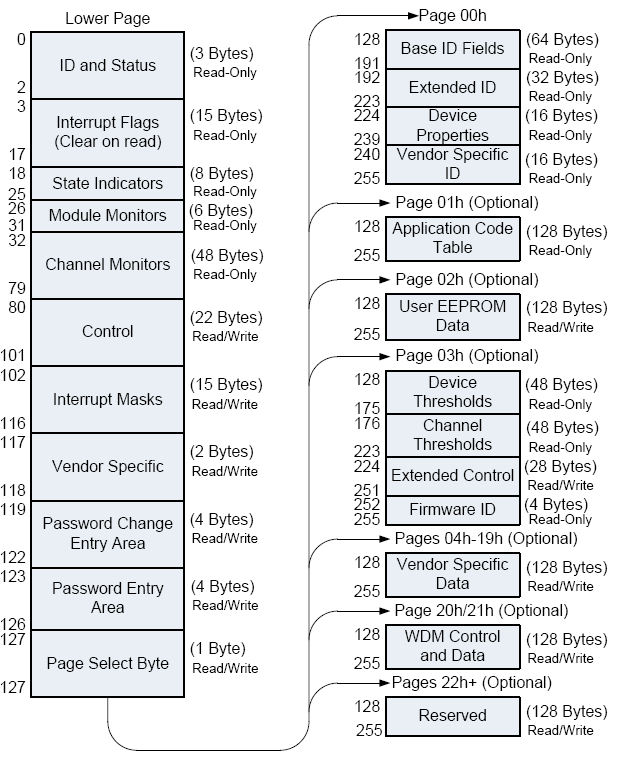

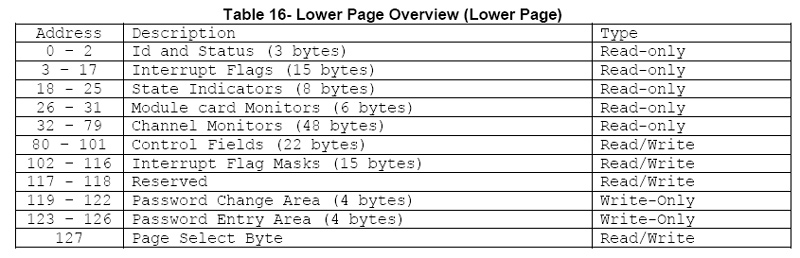

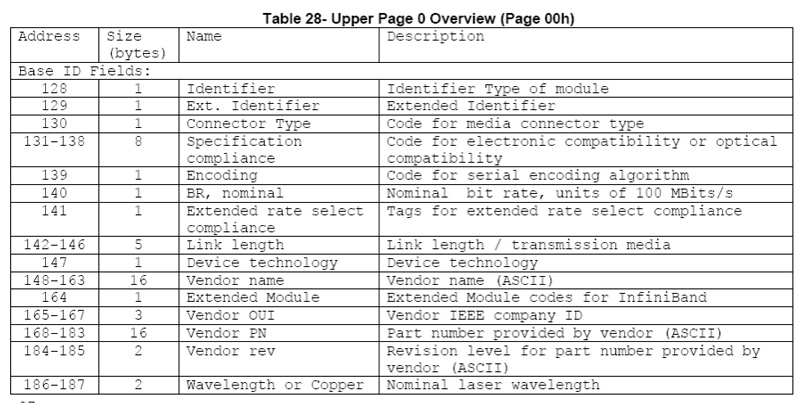

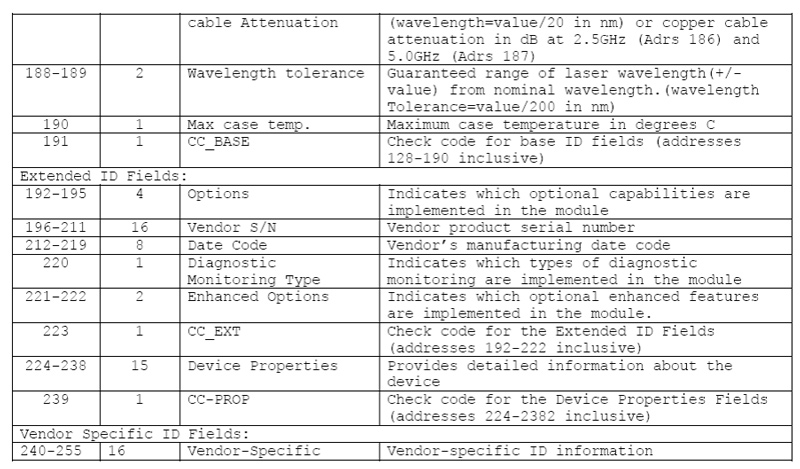

La fonction de surveillance des diagnostics numériques est disponible sur tous les produits QSFP DD. Une interface série à 2 fils fournit à l'utilisateur un contact avec le module. La structure de la mémoire est illustrée à la figure 5. L'espace mémoire est disposé en une seule page inférieure, un espace d'adressage de 128 octets et plusieurs pages d'espace d'adressage supérieur. Cette structure permet d'accéder en temps opportun aux adresses de la page inférieure, par exemple. Interrompre les drapeaux et les moniteurs. Moins d'entrées critiques dans le temps, par exemple les informations d'identification série et les paramètres de seuil, sont disponibles avec la fonction Sélection de page. La structure fournit également une extension d'adresse en ajoutant des pages supérieures supplémentaires si nécessaire. L'adresse d'interface utilisée est A0xh et est principalement utilisée pour les données critiques dans le temps comme le traitement des interruptions afin d'activer une lecture unique pour toutes les données liées à une situation d'interruption. Après qu'une interruption, IntL, a été affirmée, l'hôte peut lire le champ de drapeau pour déterminer le canal et le type de drapeau affectés.

Figure 5. Carte mémoire QSFP DD

Figure 6. Carte mémoire faible

Figure7. Page 00 Carte mémoire

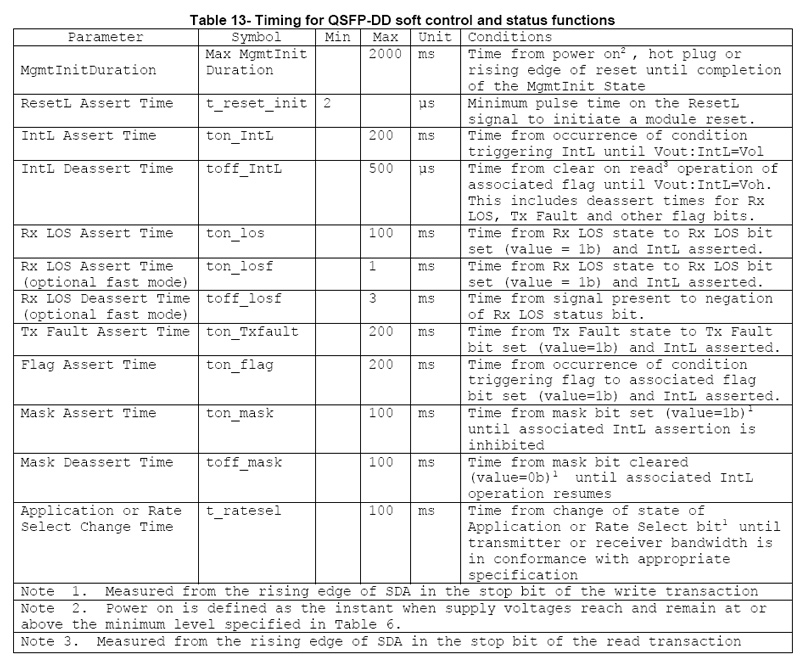

Timing pour le contrôle doux et les fonctions d'état

Figure 9. Spécifications du calendrier

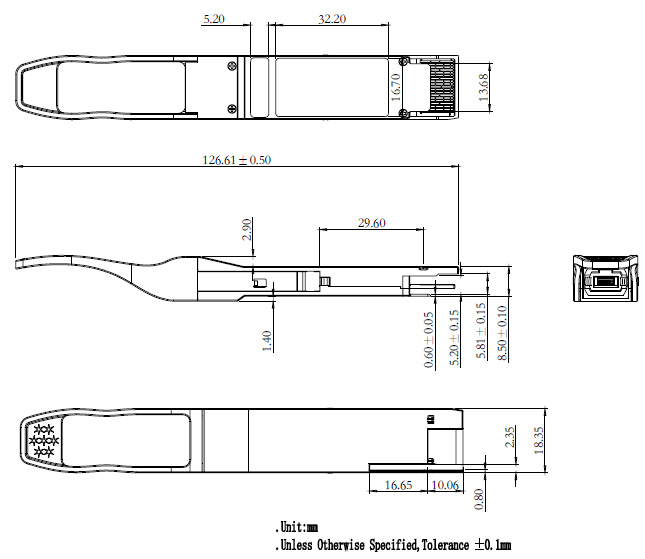

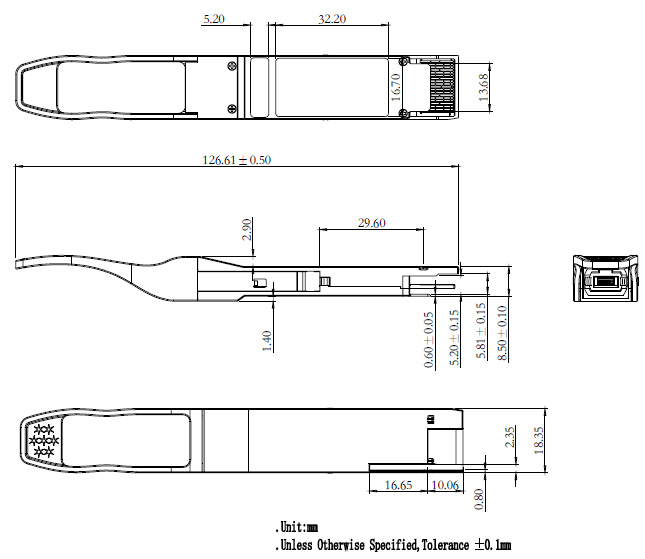

Dessin de contour (mm)

Évaluations maximales absolues

Paramètre | Symbole | Min | Max | Unité |

Tension d'alimentation | Vcc | -0.3 | 3.6 | V |

Tension d'entrée | Vin | -0.3 | Vcc + 0.3 | V |

Température de stockage | Tst | -20 | 85 | °C |

Température de fonctionnement du boîtier | Haut | 0 | 70 | °C |

Humidité (sans condensation) | Rh | 5 | 95 | % |

Conditions de fonctionnement recommandées

Paramètre | Symbole | Min | Typique | Max | Unité |

Approvisionnement Tension | Vcc | 3.13 | 3.3 | 3.47 | V |

Fonctionnement Cas Température | Tca | 0 |

| 70 | °C |

Taux de données Par voie | Fd |

| 25.78125 |

| Gbps |

Humidité | Rh | 5 |

| 85 | % |

Dissipation de puissance | Pm |

|

| 4 | W |

Spécifications électriques

Paramètre | Symbole | Min | Typique | Max | Unité |

Différentiel Entrée Impédance | Zin | 90 | 100 | 110 | Ohm |

Différentiel Sortie Impédance | Zout | 90 | 100 | 110 | Ohm |

Différentiel Tension d'entrée Amplitude AAmplitude | ΔVin | 300 |

| 1100 | MVp-p |

Sortie différentielle Amplitude de tension | ΔVout | 500 |

| 800 | MVp-p |

Skew | Sw |

|

| 300 | Ps |

Taux d'erreur de bit | BER |

|

| 5E-5 |

|

Logique d'entrée Niveau élevé | VIH | 2.0 |

| VCC | V |

Logique d'entrée Niveau faible | VIL | 0 |

| 0.8 | V |

Logique de sortie Niveau élevé | VOH | VCC-0.5 |

| VCC | V |

Logique de sortie Niveau faible | VOL | 0 |

| 0.4 | V |

Remarque:

1. BER = 5E-5; PRBS 2 ^ 31-1@25.78125Gbps. Pré-FEC

2. L'amplitude de tension d'entrée différentielle est mesurée entre TxnP et TxnN.

3. L'amplitude différentielle de la tension de sortie est mesurée entre RxnP et RxnN.

Caractéristiques optiques

Tableau 3-Caractéristiques optiques

Paramètre | Symbole | Min | Typique | Max | Unité | Notes |

Émetteur |

Longueur d'onde du centre | Λc | 840 | 850 | 860 | Nm | - |

Largeur spectrale RMS | ∆Λ | - | - | 0.6 | Nm | - |

Puissance de lancement moyenne, Chaque voie | Pout | -8.4 | - | 2.4 | DBm | - |

Modulation optique Amplitude (OMA), chaque voie | OMA | -6.4 |

| 3 | DBm | - |

Émetteur et Oeil de dispersion Fermeture (TDEC), chaque voie | TDEC |

|

| 4.3 | DB |

|

Rapport d'extinction | ER | 3 | - | - | DB | - |

Lancement moyen Puissance de OFF Émetteur, Chaque voie |

|

|

| -30 | DB | - |

Masque pour les yeux Coordonnées: X1, X2, X3, Y1, Y2, Y3 | VALEURS DE SPÉCIFICATION {0.3,0.38,0.45,0.35,0.41.0.5} | Hit Ratio = 5x10-5

|

Récepteur |

Longueur d'onde du centre | Λc | 840 | 850 | 860 | Nm | - |

Récepteur stressé Sensibilité dans l'OMA |

|

|

| -5.2 | DBm | 1 |

Moyenne maximale Puissance au récepteur, Chaque voie Entrée, chaque voie |

|

|

| 2.4 | DBm | - |

Moyenne minimale Puissance au récepteur, Chaque voie

|

|

|

| -10.3 | DBm |

|

Réflectance Récepteur |

|

|

| -12 | DB | - |

LOS Assert |

| -30 |

|

| DBm | - |

LOS De-Assert-OMA |

|

|

| -7.5 | DBm | - |

LOS Hystérésis |

| 0.5 |

|

| DB | - |

Remarque:

1. Mesuré avec le signal de test de conformité à TP3 pour BER = 5E-5 Per-FEC

Applications

● IEEE 802.3bm 100GBASE SR4

Centre de données Internet

Centre de données Internet FAQ

FAQ Nouvelles de l'industrie

Nouvelles de l'industrie À propos de nous

À propos de nous Commutateur de centre de données

Commutateur de centre de données  Commutateur d'entreprise

Commutateur d'entreprise  Interrupteur industriel

Interrupteur industriel  Interrupteur d'accès

Interrupteur d'accès  Réseau intégré

Réseau intégré  Module optique et câble

Module optique et câble

Appelez-nous sur:

Appelez-nous sur:  Nous envoyer un courriel:

Nous envoyer un courriel:  2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.